어떤 분야든 존재 이유가 없는 것들은 없겠지만 특히 엔지니어링, 공학 설계 등과 관련된 부분에서는 특히 더 두드러질 것이다. 전자 제품 설계, 회로 설계에 있어 존재 이유가 없는 구성 요소들은 제품의 원가를 높일 뿐 아니라 관리요소 및 잠재적 고장 요소가 증가하므로 단점만 불러일으킨다. 그렇기 때문에 개발자(엔지니어, Engineer) 들은 설계 시 해당 요소가 '기능 구현에 있어 필수적인지?', '요구스펙을 만족하는지?', '요구 스펙 대비 오버 스펙은 아닌지?', 'Worst Case 대비 적절한 Margin은 확보하였는지' 등을 반드시 고려해야 될 점들이 많다.

본 문에서는 Pull-up 저항과 Pull-down 저항에 대해 이야기 한다. Pull-up 저항과 Pull-down 저항은 학문적 개념보다는 회로 설계 기술(?)에 가깝기 때문에 하드웨어 회로를 직접 설계하고 제작해본 실무 경험이 없다면 낯선 개념일 것이다. Pull-up 저항과 Pull-down 저항은 쉽게 이야기 하자면 High 신호와 Low 신호를 확실하게 출력하기 위한 가이드라고 생가하면 편하다. 자세한 내용은 하기에서 살펴보도록 하자.

1. Pull-up 저항

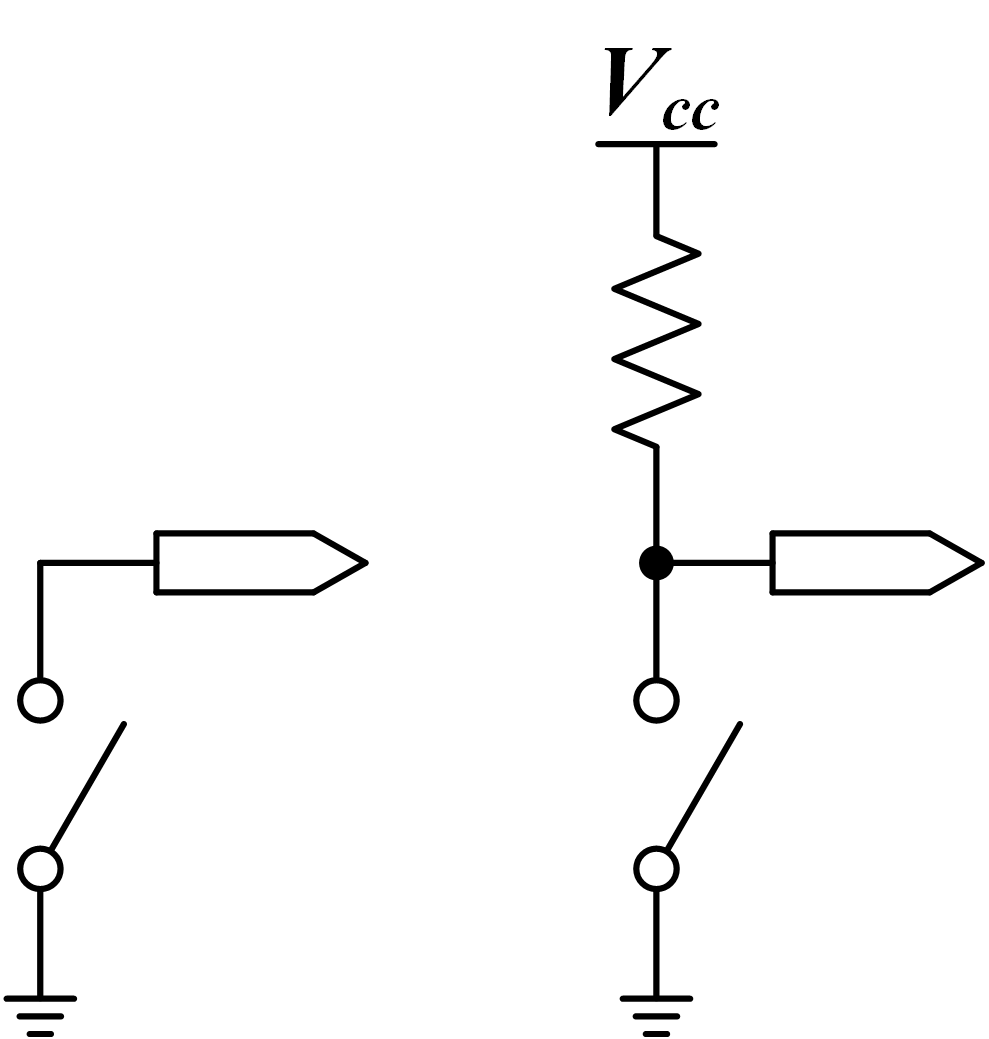

[그림 1] 은 Pull-up 저항의 유/무에 따른 기초 회로를 보여준다. 두 회로 모두 스위치가 접지단(GND or Low)와 연결되어 있으므로 스위치가 On-state 일 때 두 회로 모두 Low 신호를 출력한다. 반면 스위치가 Off-state 일 때 두 회로의 상태에서 차이가 발생하며, 이 차이로 인해 Pull-up 저항이 필요하다. 우측의 Pull-up 저항이 있을 경우 스위치가 Off-state 일 때 Vcc와 연결되어 High 신호를 출력하는 반면에 좌측의 Pull-up 저항이 없을 경우에는 스위치가 Off-state 일 때에는 상태를 알 수 없는 Floating 상태가 된다. 좌측의 Pull-up 저항이 없는 회로의 경우 스위치가 Off-state 시 출력 신호는 스위치 상단 Node의 전위가 출력된다. 그러나 해당 Node의 전위는 명확한 High 신호가 인가되지 않기 때문에 '0'전위일 수도 아닐수도 있는 것이다. 대부분의 하드웨어 회로에서 소자들은 스마트하지 않기 때문에 'Low 신호가 아닐 경우 High 신호이다'라는 식의 동작은 불가능하다. 소자들이 요구하는 On 트리거 레벨, Off 트리거 레벨에 맞는 신호를 정확히 인가해 주어야 설계자가 또는 사용자가 원하는 동작을 수행할 수 있다. 즉 Pull-up 저항은 정확한 High 신호 출력을 위해 존재한다.

2. Pull-down 저항

[그림 2]는 Pull-down 저항 유/무에 따른 기초 회로로 스위치가 On-state 일 때 High 신호가 출력된다. 그러나 스위치가 Off 되었을 때 Pull-down 저항이 없을 경우 어떤 상태가 출력될 지 모르는 Floating 상태가 된다. 즉 Pull-down 저항은 정화갛 ㄴLow 신호 출력을 위해 존재한다.

3. 필터 및 전류 제한

단순히 High 신호를 정확히 출력하기 위해서는 Pull-up 저항 없이 High 신호 전원에 직접 연결을 하고, 정확한 Low 신호 출력을 위해서라면 Pull-down 저항 없이 Low 레벨 전위(GND 등)에 직접 연결을 하면 되는 것이 아닌가? 라는 의문이 들 수 있다. 그러나 저항 없이 Vcc 또는 GND에 연결을 할 경우 과전류가 발생하여 회로의 소손을 야기할 수 있다. 그렇기 때문에 Pull-up 저항 및 Pull-down 저항의 값을 선정을 할 시에는 해당 회로의 적절 전류값을 고려하여 값을 선정한다.

4. 결론

(1) Pull-up 저항은 정확한 High 신호 출력

(2) Pull-down 저항은 정확한 Low 신호 출력

(3) Pull-up 저항 & Pull-down 저항은 과전류 제한

| Pull-up | Pull-down | |

| On-state | Low | High |

| Off-state | High | Low |

'회로설계' 카테고리의 다른 글

| SR Latch (1) / Analog 보호 회로 (0) | 2023.11.05 |

|---|