1. 시스템에서의 보호 회로

시스템에서 보호 기능은 과전류, 과전압 또는 오동작 등 예상치 못한 돌발 상황에서 부하(Load)를 보호하고, 시스템 파손을 방지하여 신뢰성을 확보하기 위한 필수 요소이다. 시스템에서 보호 기능은 크게 알고리즘에 의해 MCU (Micro Controller Unit) 입/출력 신호로 동작하는 Digital 방식과 I.C 소자 등으로 동작하는 Analog 방식으로 분류할 수 있다. Digital 방식에서는 MCU가 이상 신호 또는 고장과 같은 비정상 동작을 감지 후에 시스템 정지와 같은 보호 동작을 수행하므로 문제 발생 시점부터 보호 동작 완료까지 일정시간이 소요된다. 상황 또는 보호 프로세스 등에 따라 상이할 수 있겠으나 과전류, 과전압 같은 급박한 비상상황에서 Digital 방식에서 소요되는 시간은 시스템을 파괴하기에 충분할 수 있기 때문에 보다 빠르게 보호동작을 수행할 수 있는 Analog 방식이 요구된다. Analog 방식은 I.C 소자 등을 이용하여 이상 고장과 같은 비정상 신호 감지 시 알고리즘 같은 단계 없이 곧바로 전원을 차단하는 등의 보호동작을 수행하는데, 일정 수준 이상의 전류가 도통 되었을 때 회로를 끊어버리는 Fuse (퓨즈)가 대표적인 Analog 방식이라고 볼 수 있다. 그러나 퓨즈는 보호동작이 수행되면 해당 부품을 교환해주어야 하는 1회성 부품이라는 단점을 가지고 있다. 본문에서는 두 가지 입력과 한 가지 출력을 갖는 대표적인 Analog 보호 회로 중 하나인 SR Latch를 살펴본다. SR Latch의 두 가지 입력 포트는 문제를 감지하는 S (Set) 포트와 문제 해결 및 정상 동작 가능을 알려주는 R (Reset) 신호이며, SR Latch는 두 입력 신호를 통해 시스템의 고장을 판별한다.

2. SR Latch의 필요성

Analog 회로는 보통 기준을 설정한 후 신호가 기준보다 높은지, 낮은지 정도만 판별이 가능하다. 그러므로 Analog 회로를 이용한 보호 회로는 보통 고장 여부를 판별하는 기준을 설정한 후 해당치를 초과하거나 미달하였을 때 고장으로 인식하게 된다. 그러나 단순하게 기준치 초과, 미달 여부를 기준으로 고장여부를 판별하게 되면 치명적인 문제가 발생할 수 있는데 과전류 발생을 가정한 좌측 예시를 통해 확인이 가능하다. 고장의 원인은 다양할 수 있으나, 고장의 결과로 보여지는 현상은 주로 과전류 또는 과전압이다. 따라서 회로단에서는 과전류 또는 과전압을 감지하여 보호동작을 주로 수행하게 되는데, 이러한 과전류와 과전압은 좌측 그림과 같이 진동의 형태를 띠는 것이 보통이다. Analog 회로의 고장 기준을 A (붉은색 점선)로 설정할 경우 고장 기간 중에 기준치보다 아래로 떨어지는 구간이 발생하므로 해당 구간에서는 정상으로 판별하게 된다. 과전류가 흐르고 있는 상태에서 중간에 정상상태로 판별하여 보호 동작을 수행하지 않는다면 회로와 부하 같은 시스템에 과전류가 그대로 인가되어 보호 회로의 의미를 상실하게 된다 (붉은색 실선의 High: 고장 / 붉은색 실선의 Low: 정상). 고장 상황에서 정상 상태로 판별할 수 없도록 고장 기준을 B (파란색 점선)와 같이 설정할 경우 정상상태에서 과도구간에 발생하는 돌입 전류 등에 의해 정상상태임에도 불구하고 고장 상황으로 판별하는 오동작이 발생하게 된다 (파란색 실선의 High: 고장 / 파란색 실선의 Low: 정상). SR Latch는 이러한 문제를 해결하기 위해 최초 고장상황 식별 후 고장 신호를 출력하며, 고장 상황에서 정상 신호를 출력하지 않도록 출력 신호를 변경하기 위한 조건을 추가하여 동작한다.

3. SR Latch 동작 시나리오

SR Latch는 2개의 논리 소자로 구성된 1비트의 정보를 저장할 수 있는 순차회로이다. Active High인지, Active Low인지에 따라 구성되는 논리소자가 결정되는데 주로 Active High는 NOR 소자로 구성되고, Active Low는 NAND 소자로 구성된다. 본문에서는 시스템 회로 설계 시 SR Latch 소자를 이용하여 보호 회로를 설계 할 수 있을 정도의 수준까지 살펴볼 예정이며, Active High SR Latch와 Active Low SR Latch의 동작 분석은 추후 살펴볼 예정이다.

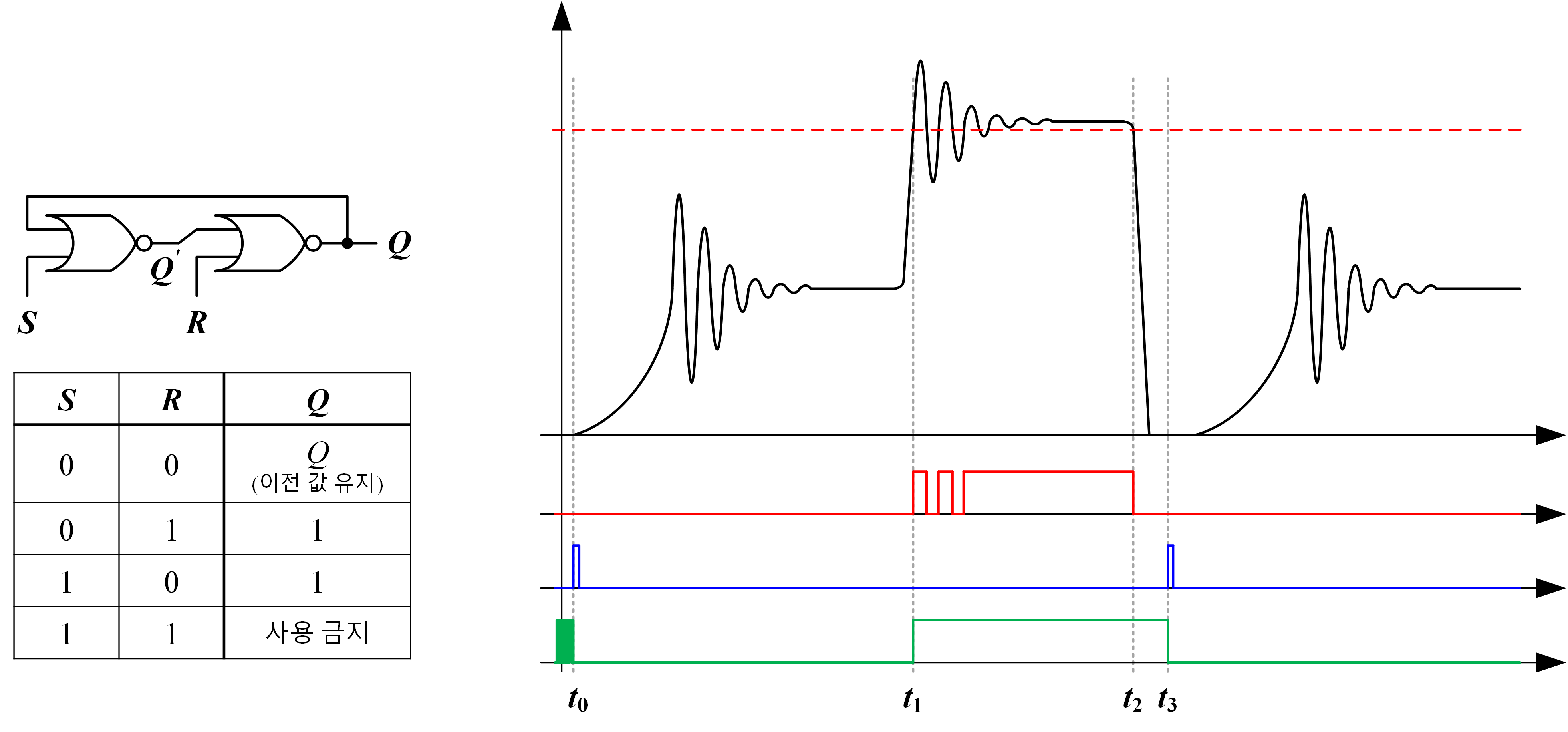

3-1. Active High SR Latch

Active High 란 활성화 신호가 High 신호로 출력되는 시스템을 말한다. 즉 과전류 보호 회로를 예시로 들면 정상상태에서 Low 였던 신호가 과전류가 발생하여 감지하게 되면 High로 바뀌는 경우를 Active High로 말할 수 있다. Active SR Latch는 고장상황을 인지하여 Latch 출력을 High로 결정하는 S (Set) 입력과 고장상황 해결 및 Run 가능 상태(정상 준비 상태)를 판별하여 Latch 출력을 Low로 결정하는 R (Reset) 입력 그리고 두 입력을 통해 고장 상황 시 High 신호를 정상 상황 시 Low 신호를 출력하는 Q 로 동작하며, 위의 그림과 같이 2개의 NOR 소자로 구성된다.

① 초기 동작 및 정상 상태 확인(~ t0)

상단의 파형은 과전류 보호를 위한 SR Latch 회로의 파형을 도시하였다. 진동하는 검은색 파형이 전류 파형이며, 시스템을 Run 하여 전류가 도통되기 전 Run이 가능한 정상상태임을 먼저 판별하게 된다. 전류가 기준(붉은색 점선)값 미만으로 있는지 여부를 확인한 후 R 신호를 High로 바꾸어주게 되면 Q는 유효한 Low 값을 출력함으로써 시스템이 정상이며 Run 할 수 있는 상태임을 보여준다.

* 시스템 고장여부 확인 구간: S = 0, R = 0 → Q = 무효값(High든 Low든 상관없음)

* 시스템 Run (동작) 가능 확인: S = 0, R = 1 → Q = 0

② 정상 동작 구간(t0 ~ t1)

R 신호에 의해 Q가 유효값을 출력하게 되면 High였던 R은 Low로 변하게 된다. R에 인가되는 High 신호는 Q의 출력을 유효값으로 바꾸거나 Low로 바꾸기 위한 신호이기 때문에 Latch 소자가 해당 R의 High 신호 입력 여부를 판별할 수 있을 정도의 시간만 High로 입력해주면 된다. 따라서 보통 DataSheet를 참고하여 R의 High 인가 신호를 결정하게 된다.

* Q 유효값 출력 후 정상상태 시: S = 0, R = 0 → Q = 0

③ 고장 상황(t1 ~ t2)

설정된 기준값(붉은색 점선) 이상으로 전류가 초과하였을 때 S는 High로 변경되게 되고 S로 인해 Q는 High 로 변경된다. 이후 S가 Low로 바뀌더라도 R이 High가 아니기 때문에 Q는 계속 고장임을 알려주는 High 신호를 출력하게 된다.

* 고장 상황 최초 식별: S = 1, R = 0 → Q = 1

* 진동 등에 의한 기준치 아래 전류 값 감지 시: S = 0, R = 0 → Q = 1

④ 고장 상황 종료 및 정상상태 확인(t2 ~ t3)

Q가 고장임을 알려주는 High 신호로 바뀜으로 인해 시스템이 보호 동작을 수행하게 되며 시스템이 정상상태로 복귀하게 되면 R에 High 신호를 인가해주게 된다. S가 Low이고 R에 High 신호가 인가되게 되면 Q는 Low로 바뀌기 때문에 시스템은 다시 Run 할 수 있는 준비 상태가 되며, 해당 상태에서 시스템은 다시 동작을 시작할 수 있게 된다.

* 고장 상황 종료: S = 0, R = 0 → Q = 1

* Run 가능 상태(정상상태) 확인: S = 0, R = 1 → Q = 0

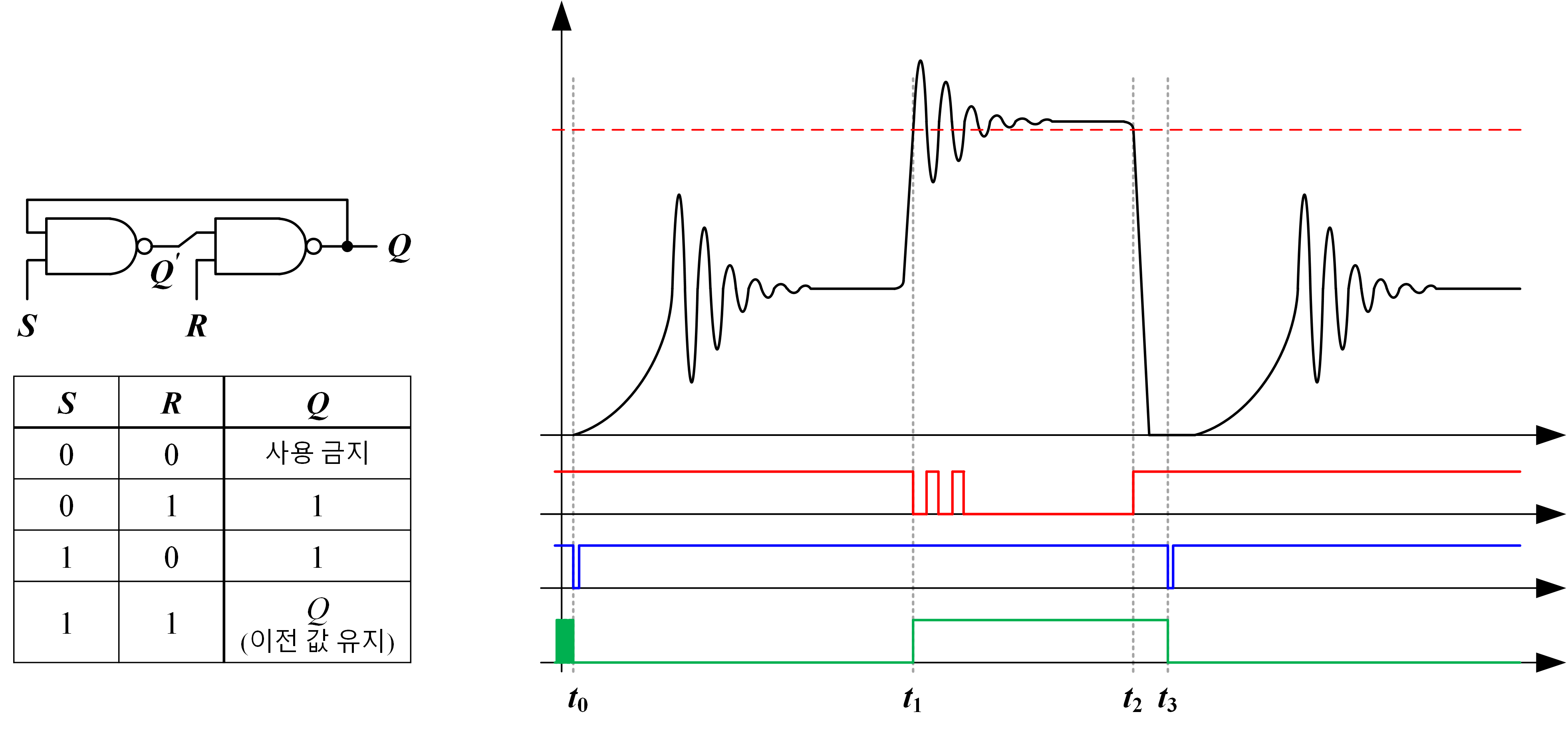

3-2. Active Low SR Latch

Active Low는 Active High와 반대로 정상상태에서 High값의 신호를 갖다가 활성화 조건에서 Low 신호로 바뀌게 되는 시스템을 말한다. Active Low SR Latch는 하기 그림과 같이 2개의 NAND 소자를 통해 구성되는데 S와 R의 신호가 Active High와 반대임을 확인할 수 있다. Active High 시스템에서는 Latch 소자 앞단에서 Open Fault 등과 같은 비정상 동작으로 인해 신호가 Low로 인가될 경우 고장을 검출하지 못하는 경우가 발생하게 되는데, Active Low의 경우 이러한 문제를 방지할 수 있다. 그러나 해당 시스템에서는 정상상태에서 상시로 High 신호가 입력되어야 하기 때문에 소모 전류(또는 전력)이 발생할 수 있는 단점이 있다.

'회로설계' 카테고리의 다른 글

| Pull-up 저항과 Pull-down 저항 / 회로설계 (0) | 2023.10.22 |

|---|